High bandwidth memory (HBM) has been around for nearly a decade and has come a long way in a short time since its initial release. With each new iteration, the data transfer speeds and capacities of HBM memories have been significantly increased. Now it is said that the new generation HBM4 memory stacks will offer very high bandwidths.

High bandwidth memory (HBM) has been around for nearly a decade and has come a long way in a short time since its initial release. With each new iteration, the data transfer speeds and capacities of HBM memories have been significantly increased. Now it is said that the new generation HBM4 memory stacks will offer very high bandwidths.HBM4 and 2048 bit interface

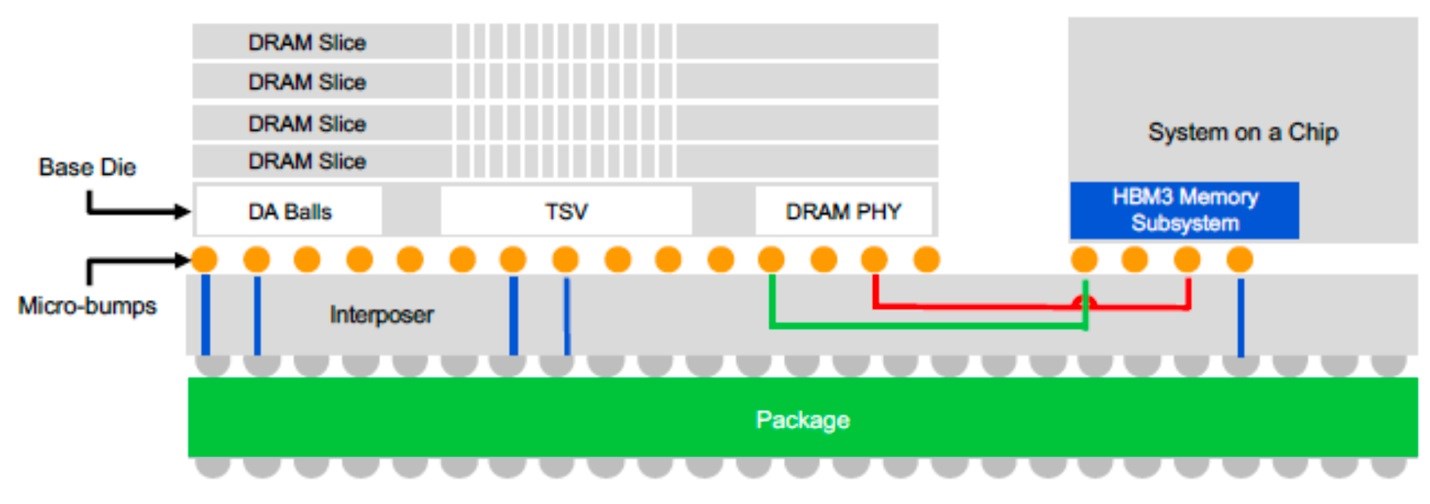

According to Seoul Economy, it is stated that the next generation HBM4 memory stacks will have a 2048-bit memory interface. We can say that increasing the interface width from 1024 bits per stack to 2048 bits per stack will be the biggest change HBM memory technology has seen to date. Because since 2015, all HBM stacks have had a 1024-bit interface. However, we should also point out that there is no official confirmation for this development, at least for now.

However, it is unclear whether memory manufacturers will be able to maintain the ~9 GT/s data transfer rates supported by HBM3E stacks for HBM4 stacks with a 2048-bit interface, but if they can, the increase in bus width will increase the peak bandwidth of 1.15 TB/s per stack. This will increase it to 2.30 TB/s per stack.

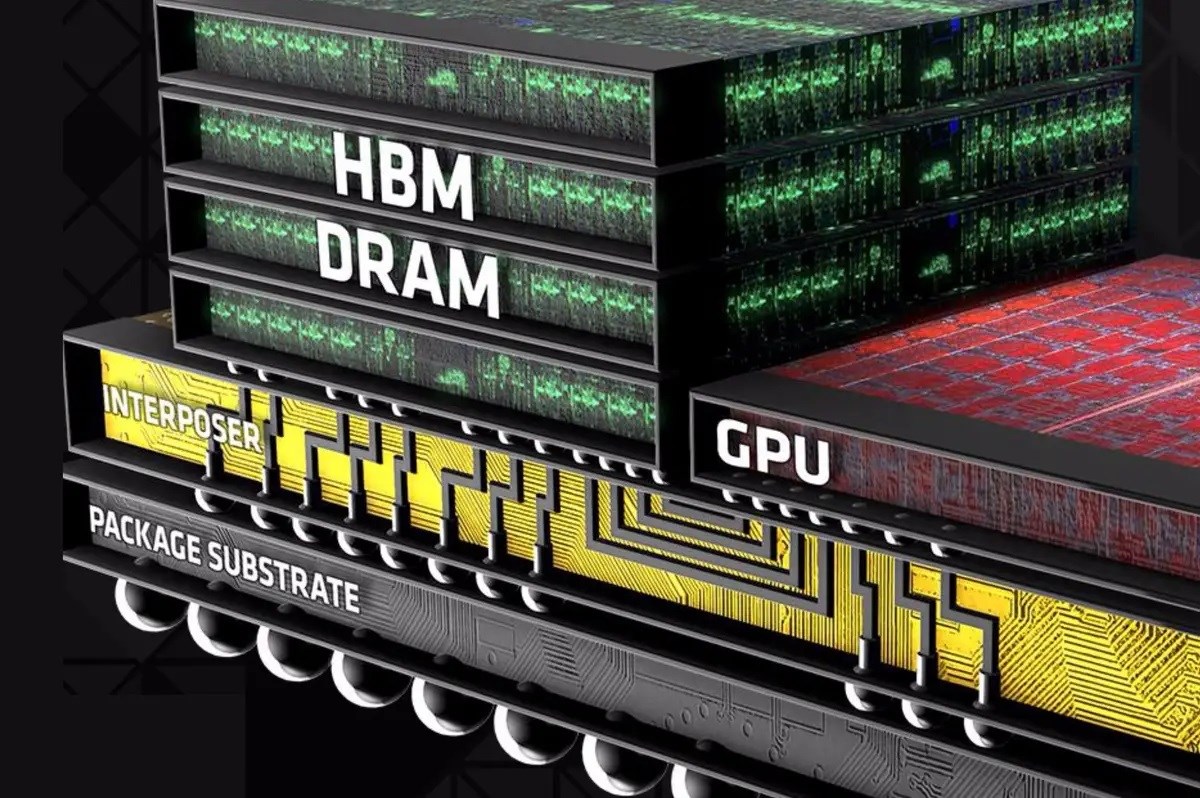

Today’s massive processors, like Nvidia’s H100, support six 1024-bit HBM3/HBM3E (also known as KGSD) dies, using a massive 6144-bit wide interface. However, if HBM’s interface width increases to 2048 bits, it is not yet clear whether processor developers will continue to use the same number of HBM4 stacks or reduce them.

Today’s massive processors, like Nvidia’s H100, support six 1024-bit HBM3/HBM3E (also known as KGSD) dies, using a massive 6144-bit wide interface. However, if HBM’s interface width increases to 2048 bits, it is not yet clear whether processor developers will continue to use the same number of HBM4 stacks or reduce them.There is also concern that the efficiency of HBM memories with 2048-bit interfaces will decrease, as it is more difficult to produce memory stacks with thousands of TSV connections, but the report states that Samsung and SK Hynix are confident that they can achieve ‘100%’ efficiency with the new memory type. For now, memory stacks with 2048-bit interfaces seem quite ambitious, but we will have more information on this subject in the future.